555定時器集成電路自1971年問世以來,憑借其穩定性高、成本低廉、功能靈活等特點,在電子設計領域占據了舉足輕重的地位。它既能作為精確的定時器,也能作為方波發生器、脈沖調制器、電壓比較器等,應用極其廣泛。本文主要探討555集成電路在定時器應用中的核心設計原理、經典電路配置及其設計要點。

一、555集成電路的核心結構與工作原理

555集成電路內部由兩個比較器、一個RS觸發器、一個放電晶體管以及一個分壓網絡(三個5kΩ精密電阻串聯,故名“555”)構成。其核心工作原理基于電容的充放電過程。通過外接電阻和電容(RC網絡)設定時間常數,內部比較器監測電容電壓,并與由分壓網絡設定的參考電壓(通常為1/3 Vcc和2/3 Vcc)進行比較,從而控制RS觸發器的狀態,最終在輸出端產生高電平或低電平。放電晶體管則在特定階段為電容提供放電通路。

二、經典定時器應用電路模式

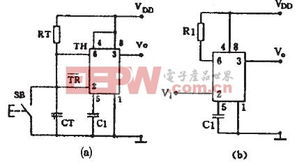

在定時應用中,555主要有兩種基本工作模式:單穩態模式和非穩態(多諧振蕩)模式。

- 單穩態模式:在此模式下,電路構成一個“一次觸發”的定時器。當觸發引腳(第2腳)接收到一個低電平脈沖(低于1/3 Vcc)時,輸出端(第3腳)會跳變為高電平并維持一段時間。該時間長度(即定時周期T)完全由外接的電阻R和電容C決定,計算公式為:T ≈ 1.1 R C。在此期間,電路對新的觸發信號不響應(除非被復位),直到定時結束,輸出恢復低電平,等待下一次觸發。此模式常用于延時開關、脈沖寬度調制、觸摸開關等。

- 非穩態模式:在此模式下,電路無需外部觸發即可自行振蕩,產生連續的矩形波(方波)輸出。它內置了充放電循環。輸出高電平時間(Thigh)和低電平時間(Tlow)由兩個電阻(R1, R2)和電容C共同決定。具體公式為:

- T_high ≈ 0.693 (R1 + R2) C

- T_low ≈ 0.693 R2 C

- 總周期 T = Thigh + Tlow,輸出頻率 f = 1 / T。

通過調節R1、R2和C的值,可以方便地獲得所需的頻率和占空比。此模式常用于時鐘信號生成、LED閃爍器、音調發生器等。

三、定時器應用設計要點與考量

設計一個基于555的可靠定時器電路,需綜合考慮以下因素:

- 定時精度與穩定性:定時周期主要依賴于RC時間常數。應選擇溫度系數小、精度高的電阻(如金屬膜電阻)和電容(如聚酯薄膜電容或鉭電容),以減小環境溫度變化帶來的誤差。電源電壓Vcc的穩定性也直接影響內部比較器的閾值電壓,進而影響定時精度,因此建議使用穩壓電源。

- 元件參數選擇:

- 電阻R:通常建議在1kΩ到幾MΩ之間選擇。阻值過小會導致電源電流過大;阻值過大(如>10MΩ)則可能因漏電流等因素導致定時不準。

- 電容C:定時電容的范圍可以從幾皮法(pF)到幾百微法(μF)。對于長定時(數分鐘至數小時),需要使用大容量電解電容,但需注意其較大的漏電流和容差會顯著影響精度,此時可考慮使用較小電容配合CMOS版本的555(如7555)以獲得更長定時。

- 觸發與復位設計:在單穩態電路中,觸發信號必須是一個短暫的低電平脈沖(寬度應小于定時時間),且需確保其電壓能可靠地降至1/3 Vcc以下。復位引腳(第4腳)通常接高電平,若需外部強制中斷定時,可將其接低電平。設計時應注意為觸發和復位信號添加適當的去抖動電路(如RC濾波或施密特觸發器),防止誤動作。

- 輸出驅動能力:標準555的輸出端可提供高達200mA的拉電流或灌電流,足以直接驅動LED、小型繼電器或揚聲器。當驅動感性負載(如繼電器線圈)時,必須在負載兩端反向并聯一個續流二極管,以吸收關斷時產生的反向感應電動勢,保護芯片。

- 電源去耦:為抑制噪聲和防止振蕩,應在555的電源引腳(第8腳)和地(第1腳)之間盡可能靠近芯片的位置,連接一個0.01μF到0.1μF的陶瓷去耦電容。

四、進階應用與改進

基礎電路之上,可以通過添加外部元件實現更復雜的功能。例如:

- 在單穩態模式的控制電壓端(第5腳)施加一個調制電壓,可以線性改變定時周期,實現電壓控制定時。

- 將兩個555級聯,可以構成長延時定時器或復雜的時序發生器。

- 對于需要更高精度和更低功耗的應用,可以選擇CMOS工藝的555(如ICL7555、TLC555等),其工作電流更小,輸入阻抗更高,更適合與高阻值電阻配合實現超長定時。

結論

555集成電路作為定時器,其設計核心在于理解其內部工作機制并合理配置外部RC網絡。單穩態和非穩態兩種模式為從簡單延時到連續脈沖發生的各類定時需求提供了簡潔高效的解決方案。通過精心的元件選型、穩定的電源供應和必要的抗干擾措施,設計者能夠構建出滿足廣泛需求、經濟可靠的定時電路。盡管當今微控制器在定時功能上更為靈活,但555芯片以其無需編程、即連即用的特性,在許多對成本和開發周期敏感的應用中,依然保持著不可替代的價值。