《Verilog HDL數字集成電路設計原理與應用》一書由蔡覺平教授編著,作為數字集成電路設計領域的經典教材,自出版以來深受廣大高校師生及工程師的歡迎。本書系統闡述了基于硬件描述語言Verilog HDL的數字系統設計原理、方法與工程實踐,是連接數字電路理論與現代芯片設計技術的關鍵橋梁。

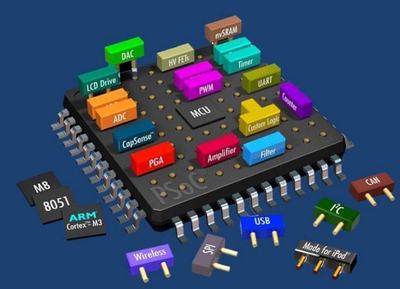

在內容編排上,本書結構清晰,循序漸進。開篇首先回顧數字電路基礎與集成電路設計流程,為后續學習奠定理論基礎。核心章節深入講解Verilog HDL的語法結構、建模方式(行為級、RTL級、門級)及可綜合設計原則。作者不僅注重語法的詳細解釋,更強調如何編寫高效、可綜合的代碼,避免初學者陷入仿真正確但無法實際實現的誤區。書中通過大量實例,如計數器、狀態機、存儲器、簡單處理器等,生動展示了從規格定義到代碼實現、功能仿真、邏輯綜合的完整設計流程。

本書的一大亮點在于其突出的應用導向。蔡覺平教授結合自身豐富的教學與工程經驗,不僅講解了語言本身,還深入探討了同步設計方法、時鐘域交叉、低功耗設計、可測試性設計等實際工程中的關鍵問題。附錄中提供的EDA工具使用指南和實驗指導,使得讀者能夠將理論知識迅速轉化為動手能力,非常適合作為高等院校電子、微電子、計算機等相關專業的教材,同時也是一線工程師不可多得的參考手冊。

在當當等圖書平臺的讀者評價中,本書普遍被認可為內容詳實、實例豐富、實用性強的優秀著作。讀者反饋其講解透徹,尤其適合Verilog HDL的入門與進階學習。盡管數字設計技術不斷發展,本書所涵蓋的核心設計思想與方法論依然具有持久的價值。對于有志于進入芯片設計領域的學子,或是希望系統鞏固數字設計知識的工程師而言,潛心研讀《Verilog HDL數字集成電路設計原理與應用》無疑將獲得扎實的技能儲備與清晰的設計視野,從而在集成電路這一技術高地上行穩致遠。